Difference between revisions of "Logic"

From #openttdcoop wiki

(This is an edit summary) |

(→Advanced logic elements) |

||

| (11 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

| − | OpenTTD allows to control trains with signals. The introduction of | + | OpenTTD allows to control trains with [[signals]]. The introduction of presignals allows to build more complex setups - the state of a signal (green/red) does not only depend on the following signal block, but also on other signals. For details, see the signal-article in the OpenTTD wiki [http://wiki.openttd.org/Signals]. |

| − | Presignals are frequently used to control trains in [[priorities]] and station entries. The combination with dummy | + | Presignals are frequently used to control trains in [[priorities]] and station entries. The combination with [[dummy train]]s, however, allows even more powerful constructions. Signals can be green or red, those states can be identified with 0 and 1, respectively (this is just a convention, it could be used the other way round as well). With trains and signals, it is possible to build all basic computer elements. In theory, it is possible to build a CPU in a game. You could even simulate OpenTTD ''in'' OpenTTD, if map size and computing power would not be a limit. |

| + | To keep constructions simple, most logic constructions are built out of several standard elements, called gates. Usually, those gates are separated with combo signals to avoid unplanned influences. If the setup is sensitive to the timing (train A has to arrive before train B or similar), this has to be taken into account in the design. Otherwise, logic gates can be combined in arbitrary way to get the desired output (green/red signals) based on some input (usually: train positions). | ||

| − | + | == Logic gates == | |

| − | + | There are always many ways to build gates. The constructions shown here are the most simple setups - if space is limited, it is often useful to change their shape a bit. | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

=== NOT === | === NOT === | ||

| Line 26: | Line 23: | ||

OR gates are red if and only if at least one input is red. There are two ways to implement this: An OR gate or a construction similar to a [[priority]]. The latter method requires less space, but it works only with trains in that signal block itself - you cannot combine arbitrary logic lines like that. | OR gates are red if and only if at least one input is red. There are two ways to implement this: An OR gate or a construction similar to a [[priority]]. The latter method requires less space, but it works only with trains in that signal block itself - you cannot combine arbitrary logic lines like that. | ||

{| align="center" | {| align="center" | ||

| − | || [[File:OR.png|thumb|430px|left|OR | + | || [[File:OR.png|thumb|430px|left|OR gates with different input states]] |

|| [[File:OR prio.png|thumb|430px|center|OR, built like a priority]] | || [[File:OR prio.png|thumb|430px|center|OR, built like a priority]] | ||

|- | |- | ||

| Line 33: | Line 30: | ||

== Advanced logic elements == | == Advanced logic elements == | ||

| + | [[File:XOR.png|thumb|220px|left|XOR construction, you can see the OR and NOT gate inside]] | ||

| + | [[File:Edge_detector_falling_inverted.png|thumb|220px|right|Falling edge detector (inverted). Output (right) flashes green when input (left) changes from red to green.]] | ||

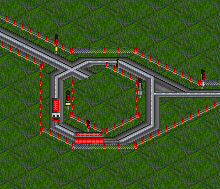

| + | [[File:Logic traincounter.png|thumb|220px|left|A simple train counter. It can fail if the line jams. The counter train (lower left part) is released if the TL2-train blocks the NOT gate entry, but not the signal block behind and in front of it.]] | ||

| + | [[File:Logic_delay.png|thumb|220px|right|A delay circuit. When the input (top right) turns green, after the train traverses the loop the output (bottom left) will flash green. The delay depends on the speed of the train.]] | ||

| + | [[File:Logic_abs_red_converter.png|thumb|220px|left|A green to absolute red converter (red PURR). The dummy train on the right alternates moves left or right depending on the input (bottom left), creating the absolute red output (bottom right). Used to make an absolute red based OR gate with the yellow line.]] | ||

=== XOR === | === XOR === | ||

XOR gates are red if exactly one of its two inputs is red. There is no known elementary gate for this, but it can be built as combination of multiple gates: (A XOR B) = (A OR B) AND (NOT(A AND B)) where A and B are the inputs. | XOR gates are red if exactly one of its two inputs is red. There is no known elementary gate for this, but it can be built as combination of multiple gates: (A XOR B) = (A OR B) AND (NOT(A AND B)) where A and B are the inputs. | ||

| Line 39: | Line 41: | ||

An edge detector is sensitive to ''changes'' of its input: If the input switches from red to green (or green to red, depending on the implementation), its output becomes green (or red) for some time, and switches back to its original position afterwards. This can be used to detect trains running on a line. | An edge detector is sensitive to ''changes'' of its input: If the input switches from red to green (or green to red, depending on the implementation), its output becomes green (or red) for some time, and switches back to its original position afterwards. This can be used to detect trains running on a line. | ||

| − | === Basic counter === | + | === Basic train counter === |

A train, running in a loop, can be used as counter: Most of the time, all signals for this train are red. To count up, all signals get green for a short time, and the train travels to the next signal. This can be used to store data, for example in [[Self-regulating Network|self-regulating networks]]. | A train, running in a loop, can be used as counter: Most of the time, all signals for this train are red. To count up, all signals get green for a short time, and the train travels to the next signal. This can be used to store data, for example in [[Self-regulating Network|self-regulating networks]]. | ||

| Line 52: | Line 54: | ||

== Applications == | == Applications == | ||

| − | |||

| − | |||

| − | |||

| − | |||

| + | === SRNW stations === | ||

| + | Stations in self-regulating networks are the most common application of logic. The trains themself cannot have a full load order, therefore it is required to control that with logic. Usually, this is done with dummy or feeder trains - they have a full load order, and SRNW trains are allowed to go into a station only if a feeder/dummy train is unloading there. | ||

| + | |||

| + | There are many possible layouts for SRNW stations, some of them are collected in the [[Junctionary_-_Stations_-_Special_Cases|Junctionary]]. | ||

| + | |||

| + | [[File:Logic forcedsplit.png|thumb|400px|right|A split for lost trains: If the SL (western exit) is free, the NOT gate switches the twoway signal on the ML to red.]] | ||

| + | === Flipflop-Split === | ||

| + | A flipflop is a small memory with two possible states. This allows splits where exactly 50% of the trains go to one side and 50% go to the other side: The flipflop stores the direction of the last train and directs the new train to the other side. | ||

| + | |||

| + | === Forced Split === | ||

| + | If trains are lost, their destination at a split can be unpredictable. With a red twoway signal, they can be forced to split in a specific direction. | ||

| + | |||

| + | <!-- | ||

=== Advanced concepts === | === Advanced concepts === | ||

*1 in 1 out (PSG239) | *1 in 1 out (PSG239) | ||

*Bigger feeder SRNW station (PZ22, PSG199) | *Bigger feeder SRNW station (PZ22, PSG199) | ||

*Self-regulating RV (PSG229) | *Self-regulating RV (PSG229) | ||

| − | |||

Things to check: [[PublicServer:Archive_-_Games_231_-_240#gameid_239|PSG239]], [[PublicServer:Archive_-_Games_221_-_230#gameid_223|PSG223]], [[PublicServer:Archive_-_Games_211_-_220#gameid_214|PSG214]], [[SRNW]] | Things to check: [[PublicServer:Archive_-_Games_231_-_240#gameid_239|PSG239]], [[PublicServer:Archive_-_Games_221_-_230#gameid_223|PSG223]], [[PublicServer:Archive_-_Games_211_-_220#gameid_214|PSG214]], [[SRNW]] | ||

| + | --> | ||

| + | |||

| + | [[Category:Advanced Networking]] | ||

Latest revision as of 21:16, 27 August 2019

OpenTTD allows to control trains with signals. The introduction of presignals allows to build more complex setups - the state of a signal (green/red) does not only depend on the following signal block, but also on other signals. For details, see the signal-article in the OpenTTD wiki [1].

Presignals are frequently used to control trains in priorities and station entries. The combination with dummy trains, however, allows even more powerful constructions. Signals can be green or red, those states can be identified with 0 and 1, respectively (this is just a convention, it could be used the other way round as well). With trains and signals, it is possible to build all basic computer elements. In theory, it is possible to build a CPU in a game. You could even simulate OpenTTD in OpenTTD, if map size and computing power would not be a limit.

To keep constructions simple, most logic constructions are built out of several standard elements, called gates. Usually, those gates are separated with combo signals to avoid unplanned influences. If the setup is sensitive to the timing (train A has to arrive before train B or similar), this has to be taken into account in the design. Otherwise, logic gates can be combined in arbitrary way to get the desired output (green/red signals) based on some input (usually: train positions).

Contents

Logic gates

There are always many ways to build gates. The constructions shown here are the most simple setups - if space is limited, it is often useful to change their shape a bit.

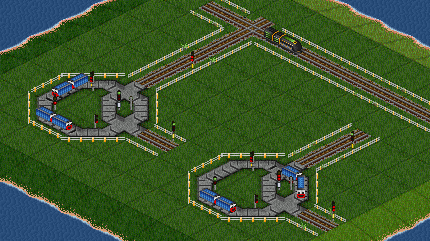

NOT

The most common logic gate you will see on coop servers is the NOT gate. It inverts the input: If the input is green, the result is red, if the input is red the result is green. This is done with two trains running on a 3x3-tile ring. If the input is green, they keep moving and at least one train keeps the output red. If the input is red, both trains stop behind an entry signal and the output is green. It is possible to use TL0.5-trains (single engine), but the gates work better with TL1-trains (two engines or double engine).

AND

AND gates are red if and only if all inputs are red. This is a feature of presignals - an entry or combo signal is red if all exit and combo signals leading to that block are red. There is no (practical) limit on the number of inputs.

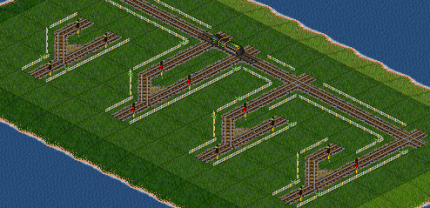

OR

OR gates are red if and only if at least one input is red. There are two ways to implement this: An OR gate or a construction similar to a priority. The latter method requires less space, but it works only with trains in that signal block itself - you cannot combine arbitrary logic lines like that.

Advanced logic elements

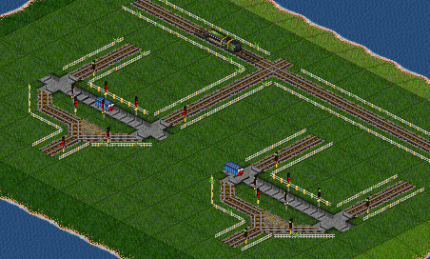

XOR

XOR gates are red if exactly one of its two inputs is red. There is no known elementary gate for this, but it can be built as combination of multiple gates: (A XOR B) = (A OR B) AND (NOT(A AND B)) where A and B are the inputs.

Edge detector

An edge detector is sensitive to changes of its input: If the input switches from red to green (or green to red, depending on the implementation), its output becomes green (or red) for some time, and switches back to its original position afterwards. This can be used to detect trains running on a line.

Basic train counter

A train, running in a loop, can be used as counter: Most of the time, all signals for this train are red. To count up, all signals get green for a short time, and the train travels to the next signal. This can be used to store data, for example in self-regulating networks.

Delay

A delay has the same output as its input, but it needs some (usually fixed) time to change the output. This can be useful if timing is important.

Red -> absolute red

A special gate to produce absolute red: A train in a signal block instead of a red presignal.

Clocks

Clocks are used to track time, for example time after the last train went through a line. See Mark's clock for an example. A very simple clock can be built with a train and a timetable to stay in a station for x days.

Applications

SRNW stations

Stations in self-regulating networks are the most common application of logic. The trains themself cannot have a full load order, therefore it is required to control that with logic. Usually, this is done with dummy or feeder trains - they have a full load order, and SRNW trains are allowed to go into a station only if a feeder/dummy train is unloading there.

There are many possible layouts for SRNW stations, some of them are collected in the Junctionary.

Flipflop-Split

A flipflop is a small memory with two possible states. This allows splits where exactly 50% of the trains go to one side and 50% go to the other side: The flipflop stores the direction of the last train and directs the new train to the other side.

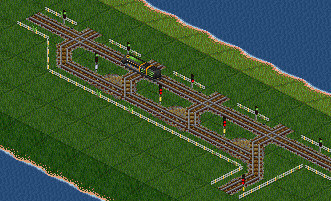

Forced Split

If trains are lost, their destination at a split can be unpredictable. With a red twoway signal, they can be forced to split in a specific direction.